31+ arm7 architecture block diagram

Shah Khushali Hemant Heena. 元器件型号为72V51356L7-5BB9的类别属于存储FIFO它的生产商为IDT Integrated Device Technology官网给的元器件描述为点击查看更多.

Arm Architecture Embedded Systems Lec 9 Bhanu Priya Youtube

Execution at maximum clock rate.

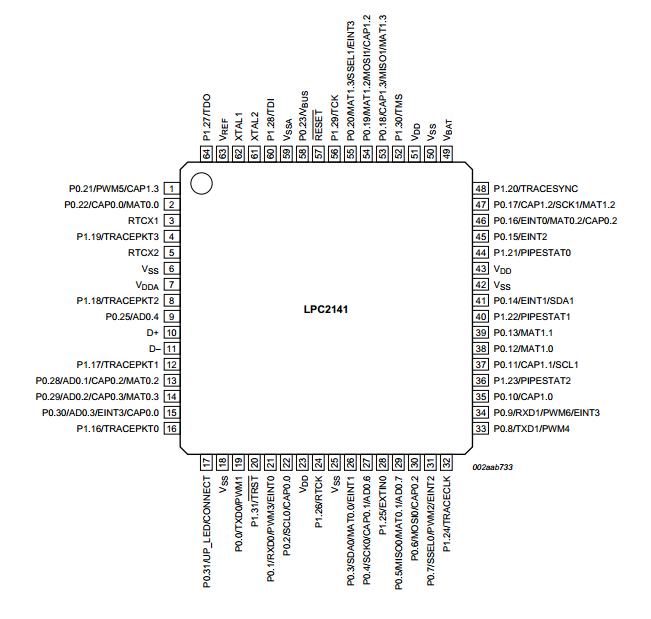

. Each FlexComm interface can be selected by software to be a USART SPI I 2 C and I2S interface. The multiplication starts whenever the beginning 04 input goes active. IOSEL2 is used to select function of Pins P116 to P131.

The below list consist of 8051. Simulation Software - PROTEUS. Automatic Extended Relationship Diagram to DB Mapper.

For critical code size applications the alternative 16-bit. 元器件型号为7P014FLA2201I15的类别属于存储存储它的生产商为White Electronic Designs Corporation厂商的官网为点击查看更多. Expert session on Hadoop Architecture 9 th Oct 19.

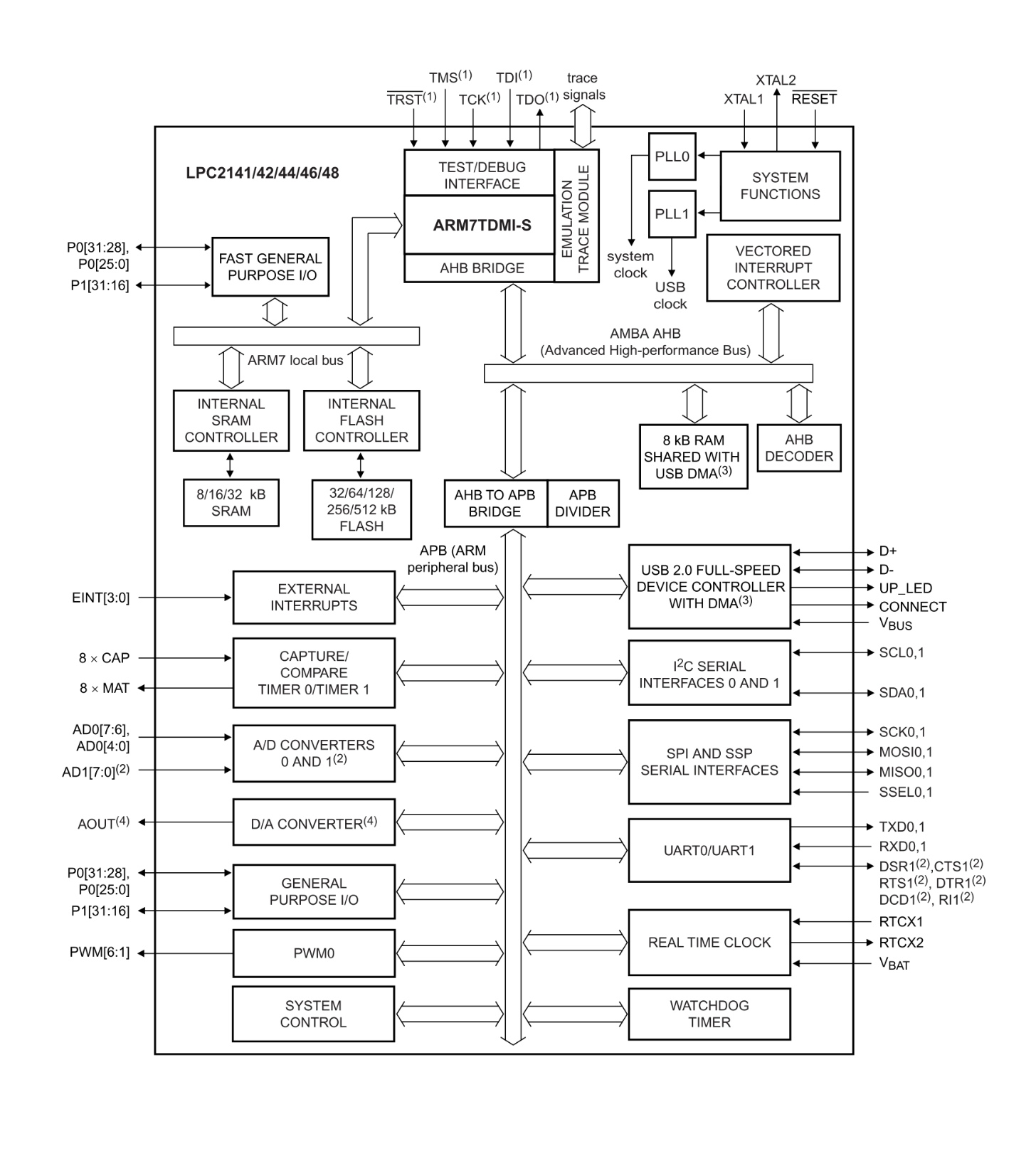

CN0079 High Precision Digital-to-Analog Conversion Using the 16-Bit AD5542AD5541 Voltage Output DAC ADR421 Reference and AD8628 Auto-Zero Op Amp X. TXD0 is a transmitter op for UART0. FlexComm interface contains up to nine serial peripherals.

All recent LPC families are based on ARM cores which NXP Semiconductors licenses from ARM Holdings then adds their own peripherals before converting the design into a silicon dieNXP is the only vendor shipping an ARM Cortex-M core in a dual in-line package. 128-bit wide memory interface and a unique accelerator architecture enable 32-bit code. The entity representation of the multiplier factor is shown in the above block diagram.

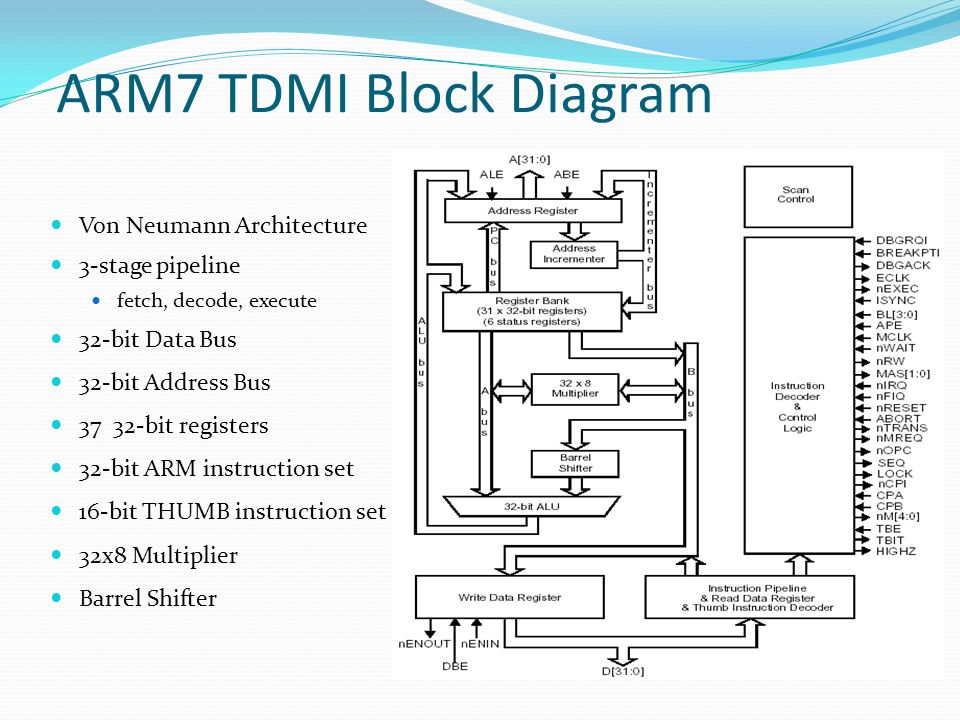

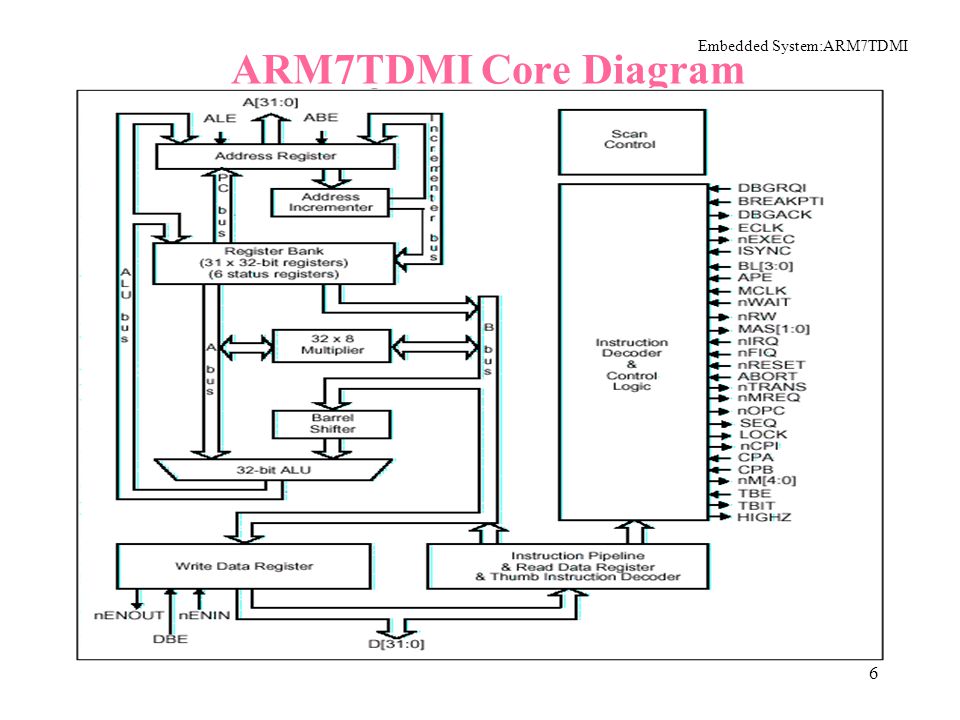

The sector mode allows for 64K byte blocks of memory. Kinetis K63K64 MCU Family Block Diagram. The ARM uses seven processing modes to.

For critical code size applications the alternative. The Cortex-M23 processor supports up to 240 interrupts compared to 32 interrupts in the Cortex-M0 and Cortex-M0 processors the exception number. P131 is a GPIO digital pin.

Compared to the Armv6-M architecture Armv8-M expanded the width of the exception number field in the Program Status Register to 9 bits. 128-bit wide memory interface and a unique accelerator architecture enable 32-bit code execution at the maximum clock rate. LPC810 in DIP8 03-inch width and LPC1114 in DIP28 06-inch width.

UP_LED is a USB good link LED indicator. By Green Hills Software Platinum Partner Test Accessories and Debugger. This device also features a sector erase architecture.

Automatic Code Generation from UML Diagram. The ARM cortex-M3 consists of 37 register sets wherein 31 are general purpose registers and 6 are status registers. 1 Output Pin 0 Input Pin.

This high-efficiency family inclusive of LPC55S69JBD100 LPC55S66JBD100 LPC55S69JEV98 LPCS66JEV98 LPC55S69JBD64 LPCS66JBD64 MCUs. Lecture on Introduction to Dynamic Programming. Kinetis K63K64 MCU Family Block Diagram.

P031 is a GPIO digital pin. I 2 C-bus interfaces support Fast-mode and fast-mode plus with data rates of up to 1 Mbits and with multiple address recognition and monitor mode. The LPC55S6x MCU family is part of the EdgeVerse edge computing platform and builds on the worlds first general-purpose Cortex-M33 based microcontroller introduced with the LPC5500 series.

PDF Rev 0 Oct 31 2012 16 MB AN4626 English Associated File. Franklin Software 8051 Development Tools. Alarm using 8051 microcontroller circuit diagram final year project report pdf b tech.

IO0DIR is used to configure pins of Port 0-P0 as input or output pins. Chawada Mayur Bhavesh Rekha. Power Architecture and ColdFire.

IO0DIR0x0000FFFF means P00 to P015 are configured as output pins and P016 to P031 are configured as. PWM1 is a pulse width modulator op-1. Block diagram 1 Pins shared with GPIO.

P00 is a GPIO digital pin. This enables the Armv8-M processor to support more interrupts. The following tables summarize the NXP.

A list of 8051 simulator softwares for free download. ARM7 local bus SCL0 SCL1 SDA0 SDA1 4 CAP0 4 CAP1 8 MAT0 8 MAT1 I2C-BUS SERIAL. When the device is arranged then it is low and when the device is not arranged then it is high.

Rayani Hiral Axay Swati. E MCU 8051 IDEThis 8051 Trainer kit has an option to connect PCs 101104 Keyboard to enter user programs in Assembly languages. The LPC553xS3x MCU family further expands the worlds first general purpose Cortex-M33-based MCU series offering significant performance enhancements all on chip RAM with Parity or ECC renewed security features and precision analog additions leveraging the cost-effective 40-nm NVM process technology.

IOSEL1 is used to select function of Pins P016 to P031.

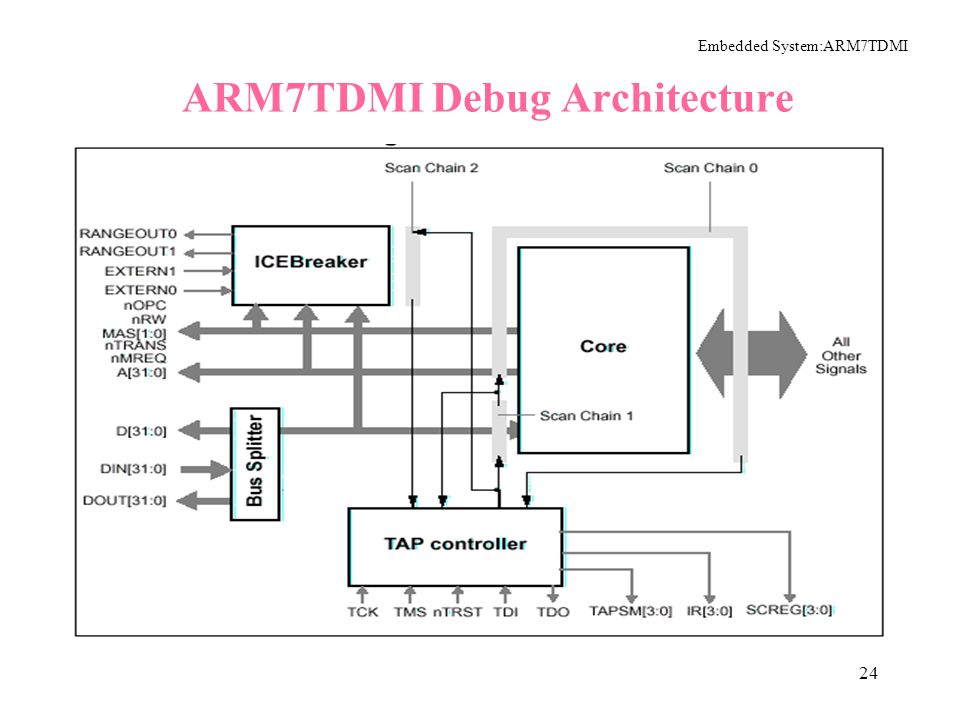

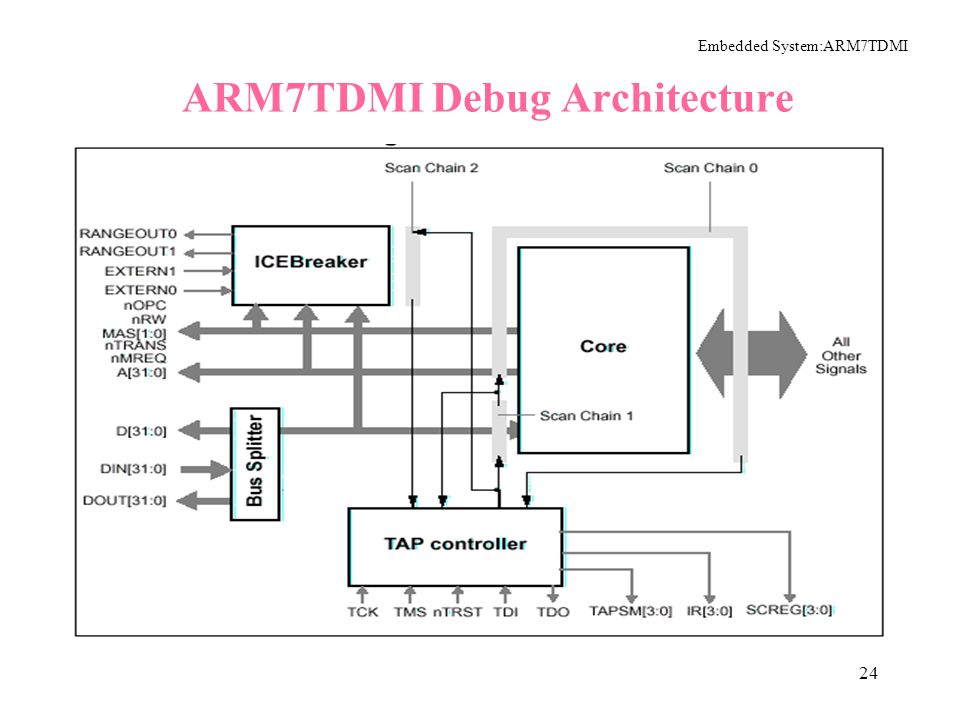

Arm7 Tdmi Introduction Ppt Video Online Download

Arm Vs Risc V Tech Journeyman

Arm7tdmi Technical Reference Manual R4p1

Arm Organization The Arm Processor Mode The Arm Architecture 8 10 Download Scientific Diagram

Arm Architecture Family Wikiwand

Arm7tdmi Technical Reference Manual R4p1

Arm7tdmi Technical Reference Manual R4p1

Stage Pipeline An Overview Sciencedirect Topics

The Arm7tdmi Hardware Architecture Ppt Video Online Download

Proposed Arm Architecture Download Scientific Diagram

The Arm7tdmi Hardware Architecture Ppt Video Online Download

The Arm7tdmi Hardware Architecture Ppt Video Online Download

The Arm7tdmi Hardware Architecture Ppt Video Online Download

Hdl How Do You Design Processors Microprocessor Not Broad Electrical Engineering Stack Exchange

Introduction To Arm7 Lpc2148 Microcontroller

Introduction To Arm Micro Controller Why Switch To Arm

Arm Architecture Working Features Eeweb